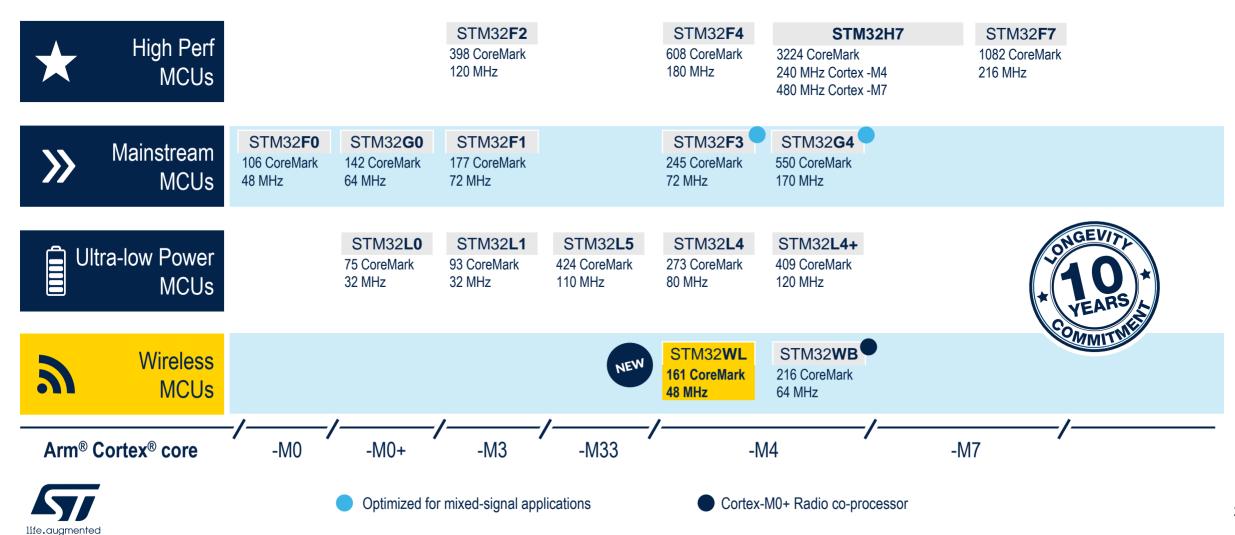

# STM32WL, 세계 최초의 LoRa 원-칩 솔루션 STM32 Discovery Day Online Track 2020

John LEE

# Agenda

Overview of LPWA Technology & Market

STM32WL World 1st LoRa SoC

Demo (Node – GTW – Server)

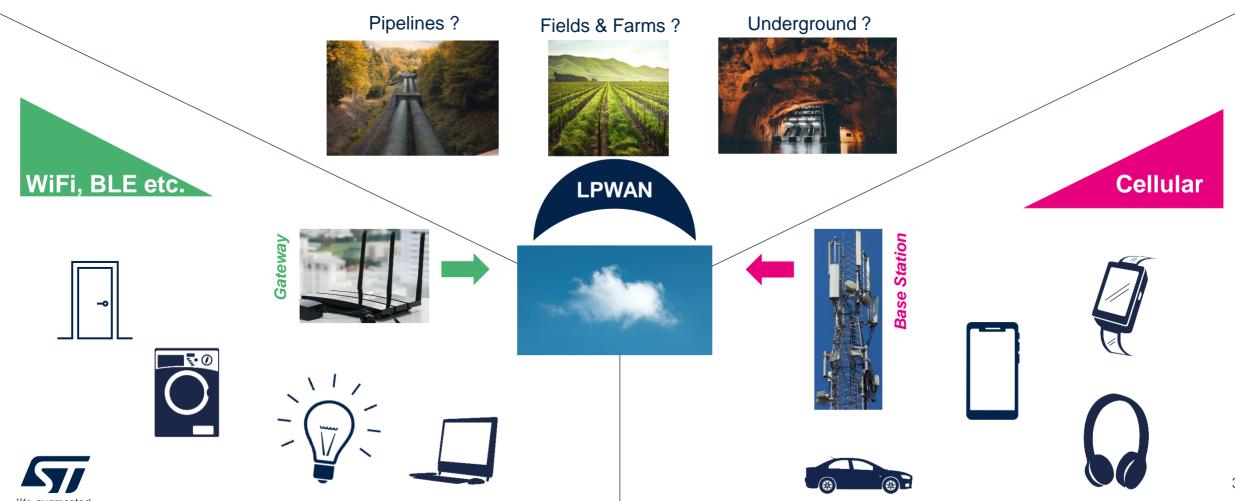

# LPWAN: The IoT missing link

### How to connect remote objects?

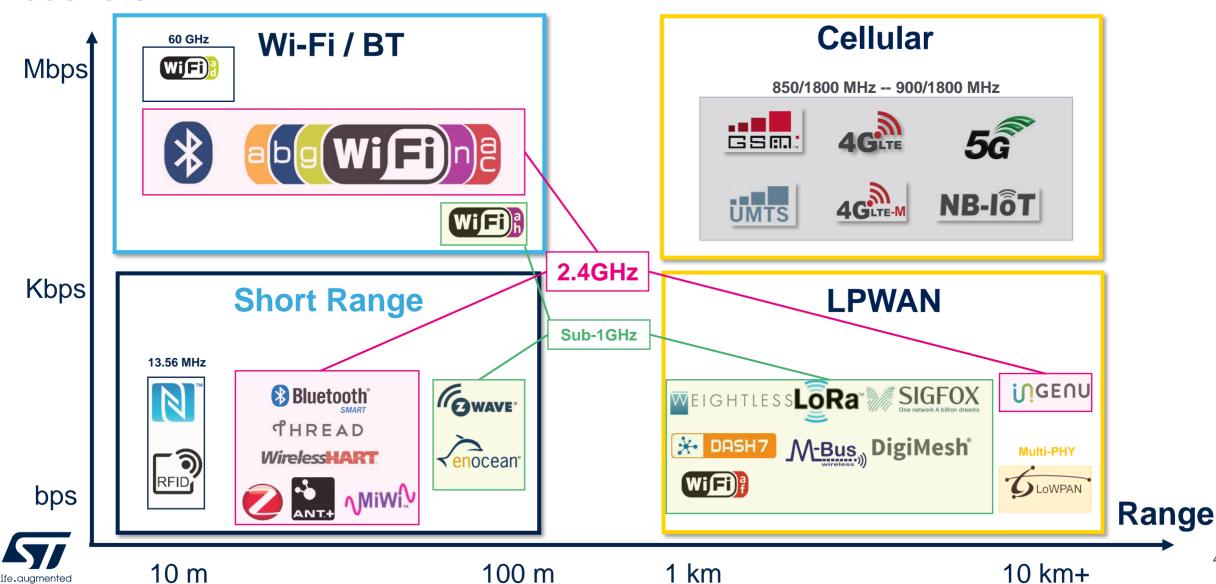

# Technological subsets overview

### **Baud rate**

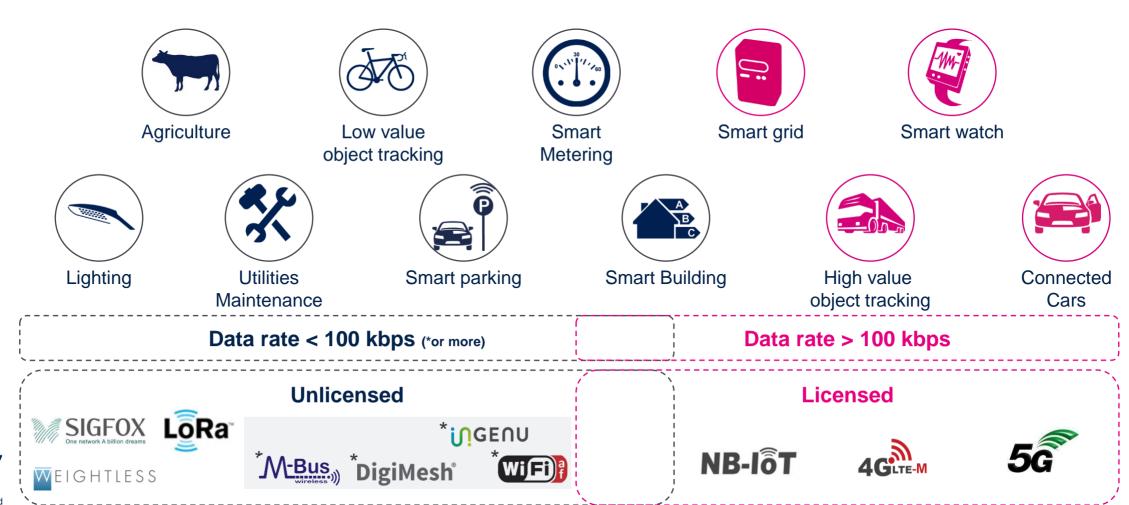

### LPWAN - Uses cases VS Data rate

### Use cases will help to identify the most appropriate technology

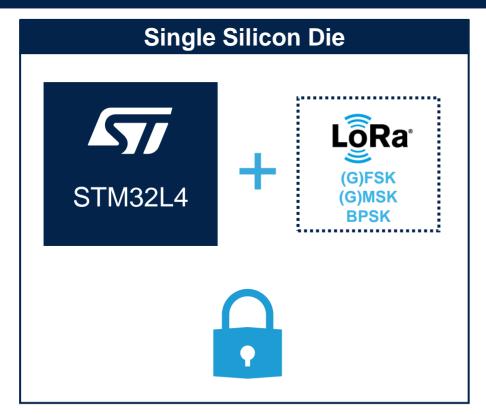

# STM32WL series MCU Long-range wireless System-on-Chip

# System-On-Chip made for versatility

### A long-range wireless microcontroller: One die, many IoT possibilities

**World First!**

### Make the choice of STM32WL series

### The 7 key points that will make the difference

Massive integration Cost saving

**Open platform**

**Ultra-low-power**

STM32 security

A large offer is coming

No matter what!

# Deep integration Wide purposes

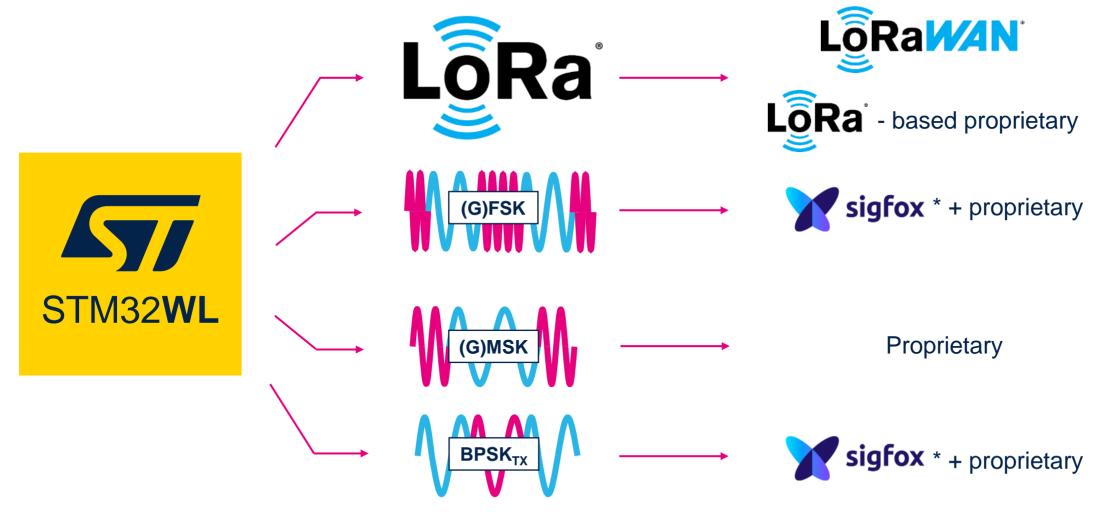

# 4 Modulations - Many protocols

### STM32WL - A rich feature set

- Arm® Cortex®-M4 DSP up to 48 MHz

- Up to 256 KB Flash and 64 KB SRAM

- Sub-GHz Radio Multi-modulations

- LoRa, (G)FSK, (G)MSK, BPSK

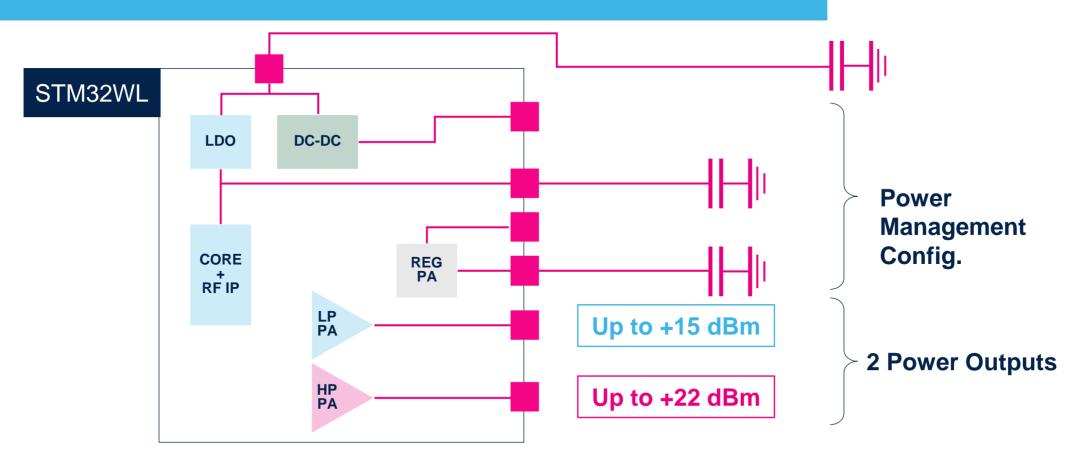

- 2 embedded power amplifiers:

1 output up to +15 dBm / 1 output up to +22 dBm

- LoRa RX sensitivity: -148 dBm (SF12, BW=10.4kHz)

- RX: 4.82 mA and TX: 15mA (at 10dBm) / 87mA (at 20dBm) [3.3V]

- Peripherals

- 3xI<sup>2</sup>C, 2xUSART, 1xLP-UART, 2xSPI

- 7x timers + 2x ULP Comparators

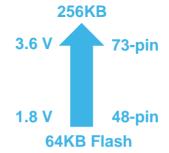

- 1.8 to 3.6V voltage range (DC/DC, LDO)

- -40 to up to +105°C temperature range

- Power consumption

- < 71µA/MHz Active mode (3V RF OFF)</li>

- 1 μA Stop2 mode with RAM retention

- 390 nA Standby mode with RTC

- 31 nA Shutdown mode

### Control

Power supply 1.8 to 3.6 V w/ DCDC+ LDO POR/PDR/PVD/BOR

Crystal oscillators 32 MHz (Radio + HSE) 32.768 KHz (LSE)

Internal RC oscillators 32,768 KHz + 16 MHz + 48 MHz ± 1% acc. over V and T(°C)

RTC/AWU/CSS

PLL/FLL

SysTick timer

2 watchdogs (WWDG/IWDG)

43 GPIOs

Cyclic redundancy check

Voltage scaling (2 modes)

#### Arm® Cortex®-M4 DSP 48 MHz

Nested vector interrupt controller (NVIC)

Memory protected unit (MPU)

JTAG/SW debug

ART Accelerator™

AHB Bus matrix

2x DMA 7 channels

#### Radio

LoRa®, (G)FSK, (G)MSK, BPSK

+15dBm & +22dBm Power Outputs -148 dBm sensitivity (LoRa)

150 MHz to 960 MHz

### **Security**

256-bit AES/PKA

TRNG + PCROP

#### Memory

Up to 256-Kbyte Flash

Up to 64-Kbyte SRAM

**Boot ROM**

Boot loader

#### Timers

1 x 32-bit timer

3x 16-bit timers 3x ULP 16-bit timers

#### Analog

1x 12-bit ADC SAR 2.5 Msps

12-bit DAC

2x ULP comparators

Temperature sensor

### Connectivity

2x SPI, 3x I2C

2x USART LIN, smartcard, IrDA, Modem control

1x ULP UART

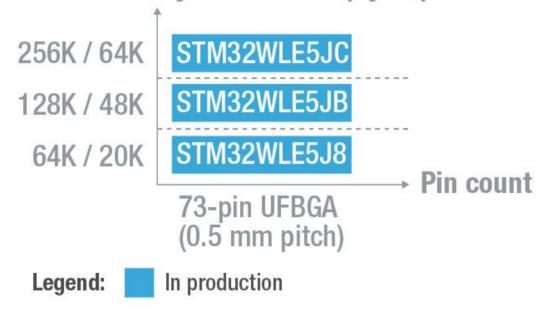

### STM32WL Sub-1 GHz - Portfolio

### Flash memory / RAM size (bytes)

Up to 43 GPIOs for full flexibility

+

Tiny package footprint

## Best Ssuited for many LPWAN markets

- Worldwide compatibility 150 MHz to 960 MHz Linear Range

- Multi-protocol capable

- ST Longevity commitment: 10 years lifetime

- Up to +22 dBm output power for wide coverage

- -148 dBm sensitivity with LoRa: Robust RF Link

- Reduced BOM cost

- Up to 105 °C MCU capable

- Only 5 µs wakeup time for best latencies

- Only 4.82 mA as LoRa RX consumption for battery optimization

- Link Budget > 160 dB = Very long ranges

- Excellent battery lifetime: Only 15 mA for LoRa TX consumption @ 10 dBm

- PCROP, ECC, TRNG, PKA, for best design robustness

- Unique-IDs for enhanced traceability

- Down to 390 nA mode with RTC and 32KB of RAM for extended Battery lifetime

- Small form factor with UFBGA 5x5 package

**Logistics**

Smart Home

- Down to 71 μA/MHz in Run mode for efficient action

- < 1 μA Stop mode with full RAM for battery life optimization

- 12-bit ADC & DAC for mixed applicative use cases

# Flexible power scheme

# Flexible power scheme FlexPowerControl

Typ with LDO @  $V_{DD} = 3 V @ 25 °C$

|       |                                  | RUN (Range1) at 48 MHz         | 71* / 115 μA / MHz     |   |

|-------|----------------------------------|--------------------------------|------------------------|---|

|       | Wake-up<br>time to RUN           | RUN (Range2) at 16 MHz         | 100* / 115 μA / MHz    |   |

|       | 6 cycles                         | SLEEP at 48 MHz                | 28* / 35 μA / MHz      | _ |

|       | 5 μs                             | STOP 1 (full retention)        | 4.55 μΑ** <sup>A</sup> |   |

|       | 5.5 µs                           | STOP 2 (full retention)        | 1 μΑ** <sup>A</sup>    |   |

|       | 29 μs                            | STANDBY + 32 KB RAM            | 445 nA** <sup>B</sup>  |   |

| 29 µs |                                  | STANDBY                        | 71 nA*                 |   |

|       | 267 μs SHUTDOW 31*** / 175 nA**B |                                | 5 nA** <sup>B</sup>    |   |

|       |                                  | V <sub>BAT</sub> 5*** / 200 n. | A**B                   |   |

|       |                                  |                                |                        |   |

<sup>\*</sup> Typical values with SMPS, RF OFF

RF Capable

### Benchmark Scores

- High Efficiency

- → CoreMark score = 162<sup>1</sup>

- Ultra Low-Power Platform

- → ULPBbench score ≈ 204<sup>1</sup>

<sup>\*\*</sup>A RTC clocked by LSI / \*\*B RTC clocked by LSE

<sup>\*\*\*</sup> All OFF

# Flexible power scheme Matching your application needs

### LPWANs made easy through ultra-low-power tradeoffs

Seamless toolbox (I<sup>2</sup>C, SPI, USART, ADC/DAC, Timers, Comparators etc.)

| Power<br>mode              | Arm <sup>®</sup><br>Cortex <sup>®</sup> -M4 | Peripherals      | RAM<br>Retention  | RF          |

|----------------------------|---------------------------------------------|------------------|-------------------|-------------|

| Run                        | ✓                                           | <b>✓</b>         | Yes               |             |

| Sleep                      | X                                           | <b>✓</b>         | Yes               | ✓           |

| Stop 0<br>Stop 1<br>Stop 2 | X<br>X<br>X                                 | √<br>✓<br>Subset | Yes<br>Yes<br>Yes | √<br>√<br>√ |

| Standby                    | X                                           | X                | Yes               | ✓           |

| Shutdown                   | X                                           | X                | Х                 | X           |

RF available In all power modes

Back-up registers are always available

# Efficient power management STOP modes comparison

### Flexible peripherals power mapping

|                    |       | STOP0                       | STOP1   | STOP2                                                                                                             |

|--------------------|-------|-----------------------------|---------|-------------------------------------------------------------------------------------------------------------------|

| Consumption        |       | Typ, 25 °C, 3 V, LDO        |         |                                                                                                                   |

| (without Real Time |       | 400 μΑ                      | 4.55 µA | 1 μΑ                                                                                                              |

| Wakeup time to     | Flash | 2.2 µs                      | 5 µs    | 5.5 µs                                                                                                            |

| 48 MHz             | RAM   | 2.2 µs                      | 5.1 µs  | 5.5 µs                                                                                                            |

| Wakeup clock       |       | ≤ 48 MHz                    |         |                                                                                                                   |

| Regulator          |       | Main or Low-Power regulator |         | Low-power regulator                                                                                               |

| Peripherals        |       | All                         | All     | CSS, RTC, 3 Tamper Pins,<br>1x LPUART, 1x I <sup>2</sup> C, VREFBUF,<br>2x COMP, 1x LPTIM,<br>Dual-WDG, CRC, EXTI |

No impact on wakeup time from embedded DCDC

# Ultra-low power & IoT ready for worldwide applications

### Best LoRa-enabled IP on the market

| Transmission |                        |               |  |

|--------------|------------------------|---------------|--|

| Parameter    | Settings               | Value         |  |

| TX           | +10 dBm<br>868/915 MHz | 15 mA<br>DCDC |  |

| TX           | +20 dBm<br>868/915 MHz | 87 mA<br>DCDC |  |

Worldwide Compatibility

| Reception            |                                                  |                                   |  |

|----------------------|--------------------------------------------------|-----------------------------------|--|

| Parameter            | Settings                                         | Value                             |  |

| LoRa<br>Sensitivity  | BW_L = 10.4 kHz<br>SF = 12                       | -148 dBm                          |  |

| 2-FSK<br>Sensitivity | BR_F = 0.6 kb/s<br>FDA = 0.8 kHz<br>BW_F = 4 kHz | -125 dBm                          |  |

| RX                   | FSK 4.8kb/s<br>buck 100mA max                    | 4.47 mA<br>DCDC<br>8.18 mA<br>LDO |  |

| RX                   | LoRa <sup>®</sup> 125 kHz                        | 4.82 mA<br>DCDC<br>8.9 mA<br>LDO  |  |

# Flexible power implementation

### Tailor STM32WL to your IoT needs

# Advanced features and ecosystem

# STM32WL - Safety and security

### Secure you application with embedded safety & security

- · Back-up clock circuitry

- Supply monitoring

- · Dual watchdog

- Flash memory with ECC (address status register)

- SRAM Parity check

- Cyclic Redundancy Check

- Brown-out reset in all modes

- Clock Security System

- Backup byte registers

### **Security**

- Anti-Tamper detection

- Boot Lock

- Read & Write protection

- Memory Protection Unit (MPU)

- Software IP Protection

- True Random Number Generator

- Private Key Accelerator

- Unique IDs (64- and 96-bit)

Management

# Chips & stacks delivery model

### Open chips, takeaway stacks

# STM32WL Arm® Cortex®-M4 Application Firmware + Peripherals + Radio stack

- Open Platform

- Open stack

**Certified LoRaWAN stack**

# A higher level of integration

### MCU + Radio 2-in-1 solution

# STM32WL Arm® Cortex®-M4 Application Firmware + Peripherals + Radio stack

VS

Standalone St MCU tra

**Standalone** transceiver

- SoC solution (1 single die)

- All-in-1 solution cost saving

- Simplified development helps speeding up time to market

- 2 standalone chips, or dice (SiP)

- Bigger final PCB (increased cost)

- Wired communication more exposed

# STM32WL – Introductory ecosystem

### Fully integrated into the rich and market-proven STM32 ecosystem

### STM32 Nucleo-64

Flexible prototyping

### Dev tools

STM32CubeMX for pinout and clock configuration

STM32CubeProg

**Partners IDE**

### **Stacks**

LoRaWAN Sigfox<sup>1</sup>

<sup>1</sup> Coming soon

Please contact your nearest ST Sales Office for more information

# Save on your application cost

### Integrated functionalities helps you drop the BOM down

### **Optimization of the silicon cost**

- Deep integration factor

- Less external components

- Single 32 MHz crystal for CPU

& embedded radio

- 32 kHz master clock output available

### **Optimization of the ecosystem cost**

- LoRaWAN stack: free of charge

- STM32CubeMX: free of charge

- STM32CubeProg: free of charge

- System-on-chip avoids to use a second radio

# STM32 rolling longevity commitment

### Longevity commitment is renewed every year

**Starting in 2020**

STM32F1 (launched in 2007)STM32L1 (launched in 2009)

STM32F2 (launched in 2010)

•

• STM32WB (launched in 2018)

• STM32G0 (launched in 2018)

• **STM32G4** (launched in **2019**)

STM32WL (launched in 2020)

22 years of commitment

20 years of commitment

19 years of commitment

11 years of commitment

11 years of commitment

10 years of commitment

10 years of commitment

### STM32 MCU "Wireless" Series

# Releasing Your Creativity

/STM32

@ST\_World

community.st.com

www.st.com/STM32WL

# Thank you